Die Erfindung des Transistors hat die Elektronik revolutioniert.

Die Geburt des Transistors war ein wichtiger Meilenstein in der Geschichte der Elektronik. Die Entwicklung von integrierten Schaltkreisen (ICs) war dann ein weiterer wichtiger Schritt.

Leiterplatttenlexikon

Leiterplattenlexikon

Begriffe im Zusammenhang mit dem Leiterplattenentwurf

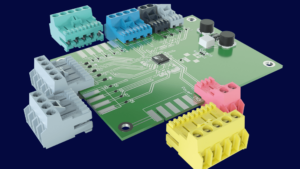

Entwickeln Sie elektronische Geräte und suchen nach Prototypen oder Kleinserien? Wir begleiten Sie von der Ideenfindung über die Entwicklung bis zur Fertigung und dem funktionsfähigen Muster. Erfahren Sie auch, welche Schritte erforderlich sind, um den Fertigungsprozess effizient zu gestalten.

Unabhängig davon, ob Sie Leiterplatten entwerfen oder bestellen: Die Vielzahl an Begriffen im Zusammenhang mit dem Leiterplattenentwurf und der Produktion kann oft unübersichtlich und verwirrend sein.

Deshalb möchten wir Ihnen eine Hilfestellung bieten: Unser neues Leiterplatten-Lexikon erklärt die wichtigsten Begriffe und wird, wo sinnvoll, durch Illustrationen ergänzt, die den Sachverhalt oft schneller verständlich machen.

Leiterplattenlexikon

- ALLE

- A

- B

- C

- D

- E

- F

- G

- H

- I

- J

- K

- L

- M

- N

- N

- O

- P

- Q

- R

- S

- T

- U

- V

- W

- X

- Y

- Z

- ABFASEN

- ABSCHIRMUNG

- ABZIEHLACK

- ADAPTERTEST

- ÄTZEN

Abfasen, auch bekannt als „Anfasen“, beschreibt das Abschrägen oder Anfasen von Kanten an Leiterplattenkonturen.

Diese Technik wird beispielsweise bei Steckverbindern angewendet, um ein leichteres Verbinden mit der Leiterplatte zu ermöglichen.

Ein weiterer Grund für das Abflachen der Kanten kann der Schutz umliegender Komponenten vor scharfen Kanten während des Einbaus sein.

Abschirmungen sind Gehäuse, die eine Leiterplatte und/oder spezifische Bereiche in den Layouts der Leiterplatte umgeben, welche ein Masse- bzw. GND-Potenzial aufweisen. Ihr Zweck besteht darin, die Übertragung von Funkstörungen (RF) und elektromagnetischer Interferenzen (EMI) von einer Leiterbahn auf eine oder mehrere andere Leiterbahnen zu verhindern.

Bei Abschirmungen für Leiterplatten kann die Schirmung beispielsweise aus einer Leiterplatte mit einer integrierten Massefläche bestehen, sowie aus Metallgehäusen (sogenannten „Board Level Shieldings“ oder BLS), die über die empfindlichen oder sendenden Elemente gelegt werden. Diese Komponenten sind dann durch einen Faradayschen Käfig isoliert und bieten somit Abschirmungseffekte.

Abziehlacke, auch bekannt als Peelable Coating, finden vor allem Anwendung beim Wellenlöten oder Schwalllöten. Sie dienen dazu, ausgewählte Bereiche auf den Leiterplatten zu schützen, die mit einer Lötwelle in Kontakt kommen.

Der Abziehlack wird auf diese Bereiche aufgetragen, um den Kontakt mit Zinn zu verhindern. Falls anschließend ein weiteres Löten dieser Bereiche erforderlich ist, kann der Abziehlack später einfach entfernt werden.

Beim Adaptertest erfolgt die elektrische Prüfung von Leiterplatten mithilfe eines speziellen Adapters. Für diesen Test muss ein Nadeladapter eingerichtet werden, der auf die spezifische Leiterplatte abgestimmt ist.

Eine Alternative zum Adaptertest ist der Fingertest, auch als Flying Probe bekannt, der jedoch deutlich langsamer ist. Im Gegensatz dazu kann der Adaptertest auch bei bereits bestückten Leiterplatten durchgeführt werden. Allerdings rentiert sich der Bau eines Adapters für den Adaptertest aufgrund des höheren Aufwands und der Kosten erst bei größeren Serien.

Ätzen ist ein Verfahren, das dazu dient, den Teil der Platine, der nicht von einer Resist-Schicht bedeckt ist, vom leitfähigen Material, meist Kupfer, zu entfernen. Dies geschieht entweder durch alkalisches Ätzen mittels Ammoniak oder saures Ätzen mit Eisen-III-Chlorid.

Vorbereitung der Platine: Zuerst wird die Platine vorbereitet, indem sie mit einer Resist-Schicht bedeckt wird. Diese Resist-Schicht schützt die Bereiche der Platine, die nicht geätzt werden sollen, vor dem Ätzmittel.

Ätzmittel anwenden: Das Ätzmittel, entweder Ammoniak für alkalisches Ätzen oder Eisen-III-Chlorid für saures Ätzen, wird auf die Platine aufgetragen. Das Ätzmittel greift das ungeschützte Kupfer an und entfernt es von der Oberfläche der Platine.

Entfernen der Resist-Schicht: Nach dem Ätzen wird die Resist-Schicht von der Platine entfernt, um die Leiterbahnen und Verbindungen freizulegen.

Reinigung: Abschließend wird die Platine gründlich gereinigt, um jegliche Rückstände des Ätzmittels zu entfernen und eine saubere Oberfläche zu gewährleisten.

- ATZRESIST

- ALUKERN PLATINEN

- ALUMINIUM KERN

- ANNULAR RING

- ANTI-PAD

Ätzresist ist das Material, das die Leiterbahnen, in der Regel aus Kupfer, vor dem Einwirken der Ätzflüssigkeit wie Ammoniak oder Eisen-III-Chlorid schützt.

Vgl. auch Resist

Alukern-Platinen, auch bekannt als IMS-Leiterplatten, sind ein- oder mehrschichtige Leiterplatten, die Aluminiumschichten im Inneren enthalten. Die Verwendung von Aluminiumkernleiterplatten ermöglicht die Integration von Kühlkörpern direkt in die Platine. Dadurch wird die erzeugte Wärme besser verteilt und abgeleitet als beispielsweise bei einer FR4-Leiterplatte.

Das Durchkontaktieren wird durch Vorbohren und Isolieren des Aluminiumträgers realisiert.

Alukern-Platinen finden hauptsächlich Anwendung in der LED-Technik und bei Hochleistungskomponenten, die eine starke Wärmeentwicklung aufweisen.

Ein Aluminiumkern ist eine in mehrschichtigen Aluminiumkern-Leiterplatten integrierte Aluminiumschicht, die dazu dient, die Wärme abzuleiten, die während des Betriebs der Bauteile entsteht.

Ein Annular Ring ist der ringförmige Bereich um eine Durchkontaktierung (auch als Via bezeichnet) auf einer Leiterplatte. Es ist der Abstand zwischen dem Rand der Durchkontaktierung und dem Rand des umgebenden Pads oder Lötaugens. Der Annular Ring spielt eine wichtige Rolle für die Zuverlässigkeit und Qualität der Durchkontaktierung, da er die elektrische Verbindung zwischen den Leiterbahnen auf verschiedenen Ebenen der Leiterplatte gewährleistet und die mechanische Stabilität der Durchkontaktierung beeinflusst. Ein ausreichend großer Annular Ring ist wichtig, um eine sichere Lötverbindung herzustellen und gleichzeitig genügend Platz für das Bohren und Herstellen der Durchkontaktierung zu bieten.

Vgl. auch Restring

Ein Anti-Pad bezeichnet eine unbestückte, freie Fläche auf einer Leiterplatte um eine Durchkontaktierung herum. Diese Fläche ist normalerweise mit Isolationsmaterial bedeckt und dient dazu, einen Abstand zwischen einer Durchkontaktierung und anderen leitenden Elementen auf der Leiterplatte zu gewährleisten, um Kurzschlüsse zu vermeiden. Das Anti-Pad sorgt dafür, dass keine elektrische Verbindung zwischen der Durchkontaktierung und den benachbarten Leiterbahnen oder Pads hergestellt wird. Es wird auch als Isolationsbereich oder Schutzbereich um eine Durchkontaktierung herum bezeichnet. Die Größe und Form des Anti-Pads können je nach den Anforderungen des Designs und den Spezifikationen der Leiterplatte variieren.

Vgl. auch Pad-Freistellung

- AOI

- ARC RESISTANCE

- ASPECT-RATIO

- AU

- AUFBAU

Au (Aurum) ist das chemische Symbol für Gold. In der Herstellung von Leiterplatten spielt Gold eine wichtige Rolle bei der Oberflächenveredelung der Platte.

Vgl. auch Gold

Arc Resistance bezieht sich auf die Fähigkeit des Isolationsmaterials auf der Leiterplatte, einen Lichtbogen zu widerstehen. Lichtbögen können auftreten, wenn es zu einem Kurzschluss oder einer Überlastung kommt, was zu einer elektrischen Entladung führt. Dieser Lichtbogen kann das Isolationsmaterial beschädigen oder zerstören, was zu einem Ausfall der Leiterplatte oder sogar zu einem Brand führen kann.

Daher ist die Arc Resistance ein wichtiger Parameter bei der Auswahl des Isolationsmaterials für Leiterplatten. Materialien mit hoher Arc Resistance bieten eine bessere Sicherheit und Zuverlässigkeit, da sie einem Lichtbogen widerstehen können, ohne beschädigt zu werden. Dies ist besonders wichtig in Anwendungen, in denen hohe Spannungen oder Ströme vorhanden sind, wie beispielsweise in der Leistungselektronik oder in Hochspannungsanwendunge.

Vgl. auch Lichtbogenfestigkeit

Aspect-Ratio (AR, englisch für „Seitenverhältnis“) bezieht sich bei Leiterplatten auf das Verhältnis zwischen der Tiefe eines gebohrten Lochs und dem Durchmesser des Bohrwerkzeugs, das für dieses Loch verwendet wird.

Die Formel lautet: Aspect-Ratio = Durchmesser des Bohrwerkzeugs (in Mikrometer) : Tiefe des Lochs, die kontaktiert werden kann (in Mikrometer)

Die Tiefe des Lochs wird ohne Berücksichtigung von Kupferbeschichtung, Lötmaske, Oberflächenbehandlung oder Positionierungsmarkierungen angegeben. Ein höheres Verhältnis macht es schwieriger, eine zuverlässige Beschichtung zu erreichen, und erhöht das Risiko von Rissen während der Bestückung der Leiterplatte aufgrund der Materialausdehnung.

Bei einem niedrigeren Verhältnis sind die Durchkontaktierungen robuster und bieten eine bessere elektrische Verbindung.

Mit Hilfe des Aspect-Ratio kann bei einem festgelegten Bohrungsdurchmesser auch die passende Leiterplattendicke berechnet werden.

Aspect-Ratio (AR, englisch für „Seitenverhältnis“) bezieht sich bei Leiterplatten auf das Verhältnis zwischen der Tiefe eines gebohrten Lochs und dem Durchmesser des Bohrwerkzeugs, das für dieses Loch verwendet wird.

Die Formel lautet: Aspect-Ratio = Durchmesser des Bohrwerkzeugs (in Mikrometer) : Tiefe des Lochs, die kontaktiert werden kann (in Mikrometer)

Die Tiefe des Lochs wird ohne Berücksichtigung von Kupferbeschichtung, Lötmaske, Oberflächenbehandlung oder Positionierungsmarkierungen angegeben. Ein höheres Verhältnis macht es schwieriger, eine zuverlässige Beschichtung zu erreichen, und erhöht das Risiko von Rissen während der Bestückung der Leiterplatte aufgrund der Materialausdehnung.

Bei einem niedrigeren Verhältnis sind die Durchkontaktierungen robuster und bieten eine bessere elektrische Verbindung.

Mit Hilfe des Aspect-Ratio kann bei einem festgelegten Bohrungsdurchmesser auch die passende Leiterplattendicke berechnet werden.

Der Aufbau von Leiterplatten kann je nach den Anforderungen des Designs variieren, aber im Allgemeinen bestehen Leiterplatten aus mehreren Lagen von Substratmaterial, die mit leitfähigen Kupferbahnen bedruckt sind. Hier ist ein typischer Aufbau für eine mehrschichtige Leiterplatte:

Innere Lagen: Diese Lagen bestehen aus einem isolierenden Substratmaterial, das oft aus Glasfaserverbundwerkstoff (FR-4) besteht. Auf beiden Seiten des Substrats sind Kupferbahnen aufgedruckt, die durch einen Prozess der Fotolithographie und Ätzung hergestellt werden. Diese inneren Lagen enthalten oft die Hauptverbindungen und Schaltungen des Designs.

Dielektrisches Material: Zwischen den inneren Lagen befindet sich dielektrisches Material, das isolierend ist und die elektrischen Verbindungen zwischen den einzelnen Lagen trennt. Dieses Material kann auch als Prepreg bezeichnet werden und ist in der Regel ein Epoxidharz.

Äußere Lagen: Auf beiden Seiten der inneren Lagen befinden sich die äußeren Lagen. Diese bestehen aus dem gleichen isolierenden Substratmaterial wie die inneren Lagen und sind ebenfalls mit Kupferbahnen bedruckt. Die äußeren Lagen enthalten oft die Anschlüsse und Schnittstellen, die mit externen Komponenten verbunden sind.

Kupferbeschichtung: Nachdem die Leiterplatte geätzt wurde, um die gewünschten Leiterbahnen zu formen, wird die gesamte Oberfläche der Leiterplatte normalerweise mit einer dünnen Schicht Kupfer beschichtet, um die Lötbarkeit zu verbessern und die Leiterbahnen zu schützen.

Lötmaske und Beschriftung: Eine Lötmaske wird über die Leiterplatte aufgebracht, um die Leiterbahnen abzudecken und sie während des Lötprozesses zu schützen. Darüber hinaus kann eine Beschriftung aufgedruckt werden, um die Komponenten zu identifizieren und das Layout zu erleichtern.

Vgl. auch Lagenaufbau

- AUSFRÄSEN

- AUSSENLAGE

- AUTOROUTER

Das Ausfräsen von Leiterplatten ist ein Verfahren, bei dem überschüssiges Material um den Umfang der Leiterplatte entfernt wird, um die Leiterplatte in die gewünschte Form zu bringen. Hier sind die Schritte für das Ausfräsen von Leiterplatten:

Vorbereitung der Leiterplatte: Zunächst wird die Leiterplatte vorbereitet, indem sie in einem größeren Panel hergestellt wird. Dieses Panel kann mehrere Leiterplatten enthalten, die später einzeln ausgeschnitten werden.

Programmierung: Ein CAD-Programm wird verwendet, um die Konturen der Leiterplatten festzulegen, die aus dem Panel ausgeschnitten werden sollen. Dieses Programm erstellt eine digitale Vorlage, die den Fräsern sagt, wo sie schneiden sollen.

Fräsen: Die Leiterplatten werden in eine Fräsmaschine geladen, die mit speziellen Fräswerkzeugen ausgestattet ist. Die Maschine liest die digitale Vorlage und führt dann präzise Schnitte entlang der vorgegebenen Konturen durch, um die Leiterplatten aus dem Panel herauszutrennen.

Entgraten und Reinigen: Nach dem Fräsen werden die Kanten der Leiterplatten oft entgratet, um scharfe Kanten zu entfernen. Anschließend werden die Leiterplatten gründlich gereinigt, um überschüssigen Staub und Rückstände zu entfernen.

Inspektion: Abschließend werden die ausgeschnittenen Leiterplatten inspiziert, um sicherzustellen, dass sie den Spezifikationen entsprechen und frei von Fehlern sind.

Das Ausfräsen von Leiterplatten ist ein wichtiger Schritt im Herstellungsprozess, der dazu beiträgt, dass die Leiterplatten die gewünschte Form und Größe haben, um in elektronischen Geräten verwendet zu werden.

Vgl. auch Fräsen

Die Außenlage bezeichnet die obere (Top) oder untere (Bottom) Schicht einer mehrschichtigen Leiterplatte.

Eine Leiterplatte kann entweder eine oder zwei Außenlagen haben, auf denen später Komponenten montiert werden können.

In jeder modernen Leiterplatten-Layoutsoftware ist ein Autorouter enthalten, der automatisch die tatsächliche Strukturierung der Leiterplatte aus einem Schaltplan generiert. Die Verbindungen zwischen den Komponenten werden in der Regel als Ratsnest dargestellt und müssen entwirrt werden.

Das Routing, also das Verlegen der Leiterbahnen zur Verbindung der Komponenten, wird automatisch durchgeführt, wobei die Designregeln (Design Roules) beachtet werden. Oft erfolgt dieser Vorgang auch interaktiv, was bedeutet, dass der Leiterplattendesigner regelmäßig in den Autorouter eingreift.

- BASISKUPFER

- BASISMATERIAL

- BAUGRUPPE

- BAUTEIL

- BAUTEILSEITE

Das Grundkupfer, auch bekannt als Erstkupfer, bezieht sich auf die Kupferschicht auf dem unbehandelten Basismaterial für Leiterplatten, wenn es beim Leiterplattenhersteller ankommt.

Diese Kupferschicht kann entweder reduziert werden, z.B. durch Ätzprozesse, oder verstärkt werden durch galvanische Kupferabscheidung.

Das Basismaterial bezeichnet die unbehandelten Rohstoffe, die beim Leiterplattenhersteller ankommen, wie zum Beispiel FR4.

Leiterplattenhersteller beziehen FR4 als Plattenmaterial und schneiden es vor Beginn der Produktion entsprechend zu. Es gibt eine Vielzahl von Basismaterialien für Leiterplatten mit unterschiedlichen Dicken, Beschichtungen sowie elektrischen und physikalischen Eigenschaften, um verschiedenen Anforderungen an die Leiterplatten gerecht zu werden. Zu den hauptsächlichen Materialien gehören FR4, Aluminium, Polyimid, Teflon (PTFE), sowie Kupfer, FR1-3 (einschließlich Pertinax®) und Keramikmaterialien wie Rogers.

Eine Leiterplatte, die mit Komponenten wie integrierten Schaltkreisen (ICs), Widerständen, Transistoren usw. bestückt ist.

Als Bauteile werden die Komponenten auf einer Leiterplatte bezeichnet, die durch Löten, Stecken usw. angebracht werden. Die meisten dieser Bauteile lassen sich in die Kategorien →SMD-Bauteile und →THT-Bauteile einordnen.

Die Bauteilseite, auch als Top-Lage oder Component-Layer bezeichnet, ist die Seite der Leiterplatte, auf der die Bauteile montiert werden.

Früher wurden Leiterplatten nur einseitig bestückt, wobei die obere Lage als Bauteillage bekannt war und die Unterseite (Leiterseite) ausschließlich für Leiterbahnen genutzt wurde. Heutzutage können Leiterplatten jedoch beidseitig bestückt werden, wodurch die Bezeichnung „Bauteilseite“ weniger eindeutig ist.

- BELICHTEN

- BESTÜCKUNG

- BESTÜCKUNGSDRUCK

- BESTÜCKUNGSPLAN

- BESTÜCKUNGSSEITE

Das Belichten ist vor allem in der traditionellen Leiterplattenherstellung erforderlich. Es wird sowohl beim Belichten des →Resists vor dem Ätzen als auch beim Belichten des Lötstopplacks nach dessen Aufbringen auf die Platine angewendet.

Heutzutage werden meist →Direktbelichter verwendet, die das Leiterplattenbild direkt auf die zu belichtende Platte projizieren, wodurch der Einsatz eines Films zur Belichtung überflüssig wird

Bestückung bezeichnet das Anbringen von Komponenten auf der Leiterplatte. Die Leiterplatte dient dabei als Basis und fungiert als Träger der Bauteile und Verbindungselemente.

Der Bestückungsdruck bezieht sich auf eine Farbe (Lack), die verwendet wird, um Positionen, Beschriftungen und Abbildungen auf der Leiterplatte anzubringen. Er wird auch häufig als Positionsdruck (Posi) oder Kennzeichnungsdruck bezeichnet. In den meisten Fällen wird Weiß für den Bestückungsdruck verwendet, obwohl auch andere Farben wie Schwarz, Rot, Gelb, Grün usw. verfügbar sind.

Der Bestückungsdruck auf einer Leiterplatte von PCB Beta LAYOUT kennzeichnet die Umrisse der Bauteile und ihre Bezeichnung. Er wird in der Regel entweder durch Siebdruckverfahren oder mit einem speziellen Tintenstrahldrucker aufgetragen. Diese Methoden ermöglichen auch kostengünstige Einzelstückbedruckungen, da kein Film benötigt wird.

Normalerweise werden nur die Umrisse der Bauelemente gedruckt, um das manuelle Bestücken zu erleichtern, sowie die Bezeichnung der einzelnen Bauteile (z. B. Durchnummerierung), um sie bei Reparaturen mithilfe des Schaltplans zu identifizieren. Auch Logos oder CE-Zeichen sind beliebt.

Siehe Bauteilseite

Siehe Bauteilseite

- BEVELING

- BGA

- BIEGEFESTIGKEIT

- BILL OF MATERIALS

- BLACK PAD

Beveling ist die englische Bezeichnung für das Abfasen oder Anfasen.

BGA (Ball Grid Array) sind eine modernere Variante von SMD-Bauteilen, bei der die Anschlüsse für die SMD-Bestückung kompakt auf der Unterseite des Bauteils angeordnet sind.

Diese Anschlüsse bestehen aus kleinen Lotperlen (englisch „balls“), die in einem regelmäßigen Raster (englisch „grid“) angeordnet sind, ähnlich einer Matrix mit Spalten und Zeilen (englisch „array“).

Beim Reflow-Löten werden diese Lotperlen geschmolzen und verbinden sich mit den Kontaktpads auf der Leiterplatte. Der Hauptvorteil liegt in der Platzersparnis, da eine größere Anzahl von Anschlüssen platziert werden kann, da sie unterhalb des Bauteils anstatt an den Seiten angeordnet sind.

Dies erschwert jedoch die spätere Überprüfung der Lötstellen, da diese nur noch durch Röntgenkontrolle überprüft werden können.

Die Biegefestigkeit, auch bekannt als Querbruchfestigkeit, bezeichnet die Spannung, die das PCB-Material aushalten kann, ohne zu brechen, wenn es in der Mitte belastet wird und auf beiden Seiten aufliegt.

Besonders bei flexiblen Leiterplatten ist die Biegefestigkeit von Bedeutung, da dort Biegeradien und die generelle Flexibilität entscheidend sind.

Die Biegefestigkeit wird in Einheiten wie kg/m2 oder psi gemessen.

Die Bauteilliste für die Bestückung von Leiterplatten, auch bekannt als BOM (Bill of Materials), ist eine Aufstellung aller benötigten Komponenten.

Black Pad, auch als „schwarzes Pad“ bezeichnet, tritt auf, wenn Chemisch Gold als Oberflächenbeschichtung auf Leiterplatten aufgebracht wird.

In solchen Fällen kann es vorkommen, dass einige Pads sich schwarz verfärben und sich nur schwer oder gar nicht löten lassen.

Ursache dafür ist eine Korrosion der Nickelschicht, die sich unter dem Gold befindet. Diese Korrosion ist vor der Bestückung mit bloßem Auge oft nicht erkennbar.

- BLASENBILDUNG

- BLEI

- BLEIFREI

- BLIND VIA

- BOHRABSTAND

Blasenbildung:

siehe auch → Delamination

Blei (chemisch „Pb“, Plumbum) oder „lead“ (Englisch) ist ein Metall, das häufig als Bestandteil von Lotlegierungen verwendet wird. Aufgrund der Einführung der →RoHS/WEEE-Norm wurde Blei größtenteils als Legierungsbestandteil verboten, da es giftig ist. Insbesondere die Dämpfe beim Löten stellen eine erhebliche Gesundheitsgefahr dar.

Heutzutage wird verbleites Lot für Leiterplatten in der Regel nur noch auf ausdrücklichen Kundenwunsch geliefert. Seit 2015 ist der Einsatz von bleihaltigem Lot in den meisten Produkten verboten und nur noch in spezifischen Anwendungsfällen gesetzlich erlaubt. Dazu gehören bestimmte Komponenten in der Automobiltechnik, Medizintechnik und Photovoltaikanlagen sowie in der Luft- und Raumfahrt, dem militärischen Bereich sowie in Forschung und Entwicklung.

Auch Hobbyanwender dürfen bleihaltiges Lot verwenden, solange sie ihre Geräte nicht in den Handel bringen.

Die Einführung von bleifreiem Lot erfolgte im Jahr 2006 und ist heute für die meisten elektronischen Anwendungen obligatorisch. Es gibt jedoch Ausnahmen für bestimmte Branchen, in denen weiterhin bleihaltiges Lot verwendet werden darf.

Die Herstellung von bleifreien Leiterplatten ist mittlerweile Standard in der Leiterplattenproduktion. Die Prozesse und verwendeten Materialien wurden erfolgreich an die vor allem höheren Löttemperaturen angepasst.

Blind Vias sind Bohrungen in der Leiterplatte, die eine Außenlage mit Innenlagen verbinden. Da sie nicht die gesamte Materialdicke durchdringen, werden sie auch als „Sacklöcher“ bezeichnet.

Diese Vias sind daher von einer Seite aus nicht sichtbar. Je nach Bohrdurchmesser und Tiefe (siehe →Aspekt-Ratio) bringen Blind Vias unterschiedliche Herausforderungen mit sich.

Wenn Innenlagen miteinander verbunden sind, ohne Kontakt nach außen zu haben, spricht man von „Buried Vias“.

Der Begriff Bohrabstand bezieht sich auf den Abstand zwischen zwei Bohrungen auf einer Leiterplatte.

Der Bohrabstand ist ein entscheidendes Merkmal, da bei Unterschreitung der Mindestabstände der Steg zwischen den Bohrungen brechen kann.

Beim Bohren besteht immer eine gewisse Toleranz. Der Bohrer kann durch Bestandteile des Laminats (wie Glasgewebe, Gewebe oder Keramik) abgelenkt werden, was zu einer Verschiebung der Bohrposition führt und den Bohrer möglicherweise zu nah an eine benachbarte Bohrung bringen kann.

Diese Möglichkeit sollte bereits während des Designs berücksichtigt werden, indem man sich an die in den Designregeln festgelegten Abstände hält und ausreichend große Abstände wählt.

Die minimale Distanz beträgt bei den meisten Leiterplattenherstellern etwa 0,2 mm, obwohl dies von Hersteller zu Hersteller variieren kann. Auch die Bohrtechnik spielt eine Rolle, da bei NDK-Bohrungen der Bohrabstand kleiner sein kann.

- BOHREN

- BOHRPROGRAMM

- BOHRUNG

- BOM

- BOTTOM

Das Bohren ist erforderlich für die Herstellung von Fanglöchern, Durchkontaktierungen und Bauteilbohrungen auf Leiterplatten. Es ermöglicht die Verbindung der Schichten (Lagen) und das Einsetzen von Bauteilen zu einem späteren Zeitpunkt.

Bei ein- und doppelseitigen Leiterplatten erfolgt dieser Prozess unmittelbar nach dem Zuschnitt. Bei mehrschichtigen Leiterplatten hingegen erfolgt das Bohren erst nach der Laminierung. Zunächst müssen die Innenlagen strukturiert und verpresst werden, bevor sie gebohrt werden können.

Das Bohrprogramm ist eine ASCII-Textdatei, die durch die IPC-Norm NC-349 (Computer Numerical Control Formatting for Drillers and Routers) definiert wird. Es übermittelt dem Bohrer die Koordinaten und Durchmesser der zu bohrenden Löcher auf der Leiterplatte. Zusätzlich enthält es Informationen über die Werkzeuge, die für die verschiedenen Bohrungen verwendet werden sollen. Das Bohrprogramm wird aus dem Layout der Leiterplatte abgeleitet, das die Position und Form der Bauteile und Leiterbahnen zeigt. Typischerweise wird das Bohrprogramm im Format Excellon oder Sieb & Meyer exportiert, das von den meisten Bohrmaschinen erkannt wird.

Bei der Bereitstellung von Gerber-Daten müssen diese Dateien zusammen mit den Gerberdaten an den Leiterplattenhersteller übermittelt werden.

BOM steht für „Bill Of Materials“ und bezieht sich auf die Bauteilliste für die Bestückung von Leiterplatten.

Die Erstellung der BOM kann oft zeitaufwändig sein, da die Bauteile gesucht und bestellt werden müssen.

BOM steht für „Bill Of Materials“ und bezieht sich auf die Bauteilliste für die Bestückung von Leiterplatten.

Die Erstellung der BOM kann oft zeitaufwändig sein, da die Bauteile gesucht und bestellt werden müssen.

Bottom bezeichnet die „Unterseite“ von Leiterplatten, die früher oft als Lötseite bezeichnet wurde. Damals wurden jedoch ausschließlich THT-Bauteile auf dieser Seite der Leiterplatte gelötet.

Mit der Einführung von SMD-Bauteilen ist der Begriff „Lötseite“ nicht mehr eindeutig, und „Bottom“ ist daher eine klarere Bezeichnung.

- BREAKOUT

- BURIED VIA

Breakout ist der englische Begriff für „Ausbruch“ und bezieht sich auf Bohrungen auf einer Leiterplatte, die nicht zentriert auf dem vorgesehenen Pad liegen und daraus resultieren. Für durchkontaktierte Pads (DK) ist ein ausreichender Restring erforderlich, um eine ordnungsgemäße Lötbarkeit sicherzustellen. Die Größe des Rings im Design sollte groß genug sein, um Abweichungen des Bohrers von der Mitte des Lochs auszugleichen. Wenn das Pad zu klein ist, kann es zu einem Ausbruch kommen, was zu unterbrochenen, unvollständigen Schaltungen oder unsachgemäßem Löten führen kann. Daher sehen Leiterplattenhersteller vor, dass der Restring um eine Durchkontaktierung einen größeren Durchmesser als der Bohrer haben muss, um mögliche Breakouts abzufangen.

In einigen Fällen kann ein Teardrop die Toleranz des Bohrers im Pad erhöhen, was dazu beitragen kann, den Ausschuss bei der Leiterplattenproduktion zu verringern.

Ein Buried Via (auch bekannt als vergrabene Durchkontaktierung oder vergrabene Bohrung) ist eine Durchkontaktierung innerhalb einer Leiterplatte, die mindestens zwei Innenlagen eines Multilayers miteinander verbindet, ohne die Außenlagen zu durchdringen.

Wie der Name schon sagt, ist eine vergrabene Durchkontaktierung von außen nicht erkennbar. Diese Vias können vor dem Verpressen des Multilayers gebohrt, durchkontaktiert und anschließend verschlossen werden.

Buried Vias ermöglichen eine höhere Packungsdichte, was bedeutet, dass auf einer gleichbleibenden Fläche mehr Funktionen integriert werden können. In einer Zeit, in der die Miniaturisierung immer weiter voranschreitet, kann dies ein wesentlicher Vorteil sein.

Allerdings können erhöhte Kosten entstehen, da die Produktion einen erhöhten Aufwand erfordert und zusätzliche Tests notwendig sind.

- CAD

- CAF-RESISTENZ

- CAM

- CARBON

- CASTELLATED-HOLS

CAD steht für „Computer Aided Design“. Früher wurden Leiterplatten manuell entworfen, aber heutzutage werden dafür Computer und spezielle CAD-Software verwendet. Nach dem Entwurf werden die produktionsfertigen Daten mithilfe von CAM erstellt. Anschließend erfolgt die Fertigung der Leiterplatte.

Beliebte CAD-Programme sind unter anderem EAGLE, Altium, TARGET 3001!, Autodesk Fusion 360, KiCad und viele andere.

Die Resistenz gegenüber CAF (Conductive Anodic Filament) oder CAF-Beständigkeit beschreibt die Fähigkeit eines Materials, das isoliert ist (zum Beispiel FR4), die elektromechanische Migration von metallisierten Salzen zu verhindern.

CAF bezieht sich auf die Bildung leitfähiger Verbindungen zwischen zwei Potenzialen von der Anode zur Kathode, die durch die Migration von Kupferionen entlang von Glasfasern innerhalb von Leiterplatten entsteht.

Dies kann zur Bildung von leitfähigen Pfaden und in extremen Fällen zu Kurzschlüssen führen.

Dieser Effekt tritt insbesondere bei fortschreitender Miniaturisierung und Komplexität der Leiterplatten auf und seine Erkennung und Beseitigung ist schwierig.

CAM (Computer Aided Manufacturing) bildet den Zwischenschritt zwischen der elektronischen Entwurfsphase (CAD) und dem tatsächlich hergestellten Objekt.

Die gelieferten Daten müssen in ein für die Produktion geeignetes Format umgewandelt und auf mögliche Fehler überprüft werden. Hierfür steht spezielle Software zur Verfügung.

In der Regel wird „Carbon“ als Abkürzung für „Carbon Print“ oder „Karbondruck“ verwendet. Dabei handelt es sich um ein Verfahren, bei dem Carbonlack mithilfe von Siebdruck auf die Leiterplatte aufgetragen wird.

Aufgrund seiner leitenden Eigenschaften und der hohen Härte des Materials wird Carbonlack beispielsweise als Beschichtung für Drucktaster auf der Leiterplatte eingesetzt.

engl. Bezeichnung für →Halboffene Durchkontaktierung

- CE-KENNZEICHNUNG

- CE-KONFORMITÄTSERKLÄRUNG

- CHEMISCH GOLD

- CHEMISCH NICKEL/GOLD

- CHEMISCH SILBER

Durch die CE-Kennzeichnung erklärt der Hersteller, Inverkehrbringer oder EU-Bevollmächtigte gemäß Verordnung (EG) Nr. 765/2008, dass das Produkt den geltenden Anforderungen entspricht, die in den Harmonisierungsrechtsvorschriften der Gemeinschaft über die Anbringung festgelegt sind (Artikel 2 Nummer 20). Außerdem übernimmt er die Verantwortung dafür, dass das Produkt gemäß den einschlägigen Harmonisierungsrechtsvorschriften der Gemeinschaft konform ist (Artikel 30 Absatz 3).

Die mit CE gekennzeichneten Produkte wurden jedoch nicht von einer unabhängigen Stelle überprüft. Derjenige, der das CE-Zeichen verwendet, bestätigt lediglich selbst die Konformität seines Produkts mit den einschlägigen Vorschriften.

Für die Inverkehrbringung eines Produktes in Deutschland ist eine CE-Konformitätserklärung erforderlich

Die CE-Konformitätserklärung ist eine schriftliche Bestätigung des Herstellers, dass ein Produkt die Anforderungen aller relevanten CE-Richtlinien erfüllt.

Für jedes Produkt, das unter eine EU-Richtlinie fällt, ist eine solche Erklärung notwendig. Der Hersteller muss die CE-Konformitätserklärung als Teil der technischen Dokumentation aufbewahren und auf Anfrage einer Aufsichtsbehörde vorlegen können.

Chemisch Gold, auch als Chemisch Nickel/Gold (ENIG) bekannt, ist eine Leiterplattenoberfläche. Mit der steigenden Nachfrage nach feineren Leiterbahnen und der zunehmenden Packungsdichte auf Leiterplatten wird HAL (Hot Air Leveling) immer ungeeigneter.

Chemisch Gold bietet eine hervorragende Alternative. Diese Oberfläche ist sehr plan und hat ausgezeichnete Oxidationseigenschaften. Die Zusammensetzung von Chemisch Gold beträgt 3-5 μm Nickel und 0,05-0,1 μm Gold.

Vorteile:

Sehr gut für Finepitch geeignet

Hervorragend für SMD geeignet

Sehr plane Pads, die mit HAL nicht erreicht werden können

Sehr gute Benetzbarkeit

Die Nickelschicht verstärkt mechanisch die Durchkontaktierungen und Vias und erhöht die Abriebfestigkeit

Gute Lagerfähigkeit (ca. 1 Jahr)

Nachteile:

- Höhere Kosten im Vergleich zu HAL

→Chemisch Gold

Chemisch Silber

Chemisch Silber ist eine Leiterplattenoberfläche, die Chemisch Zinn ähnelt, jedoch eine geringere Oxidation aufweist. Trotz dieser Eigenschaft ist Chemisch Silber ähnlich empfindlich, weshalb es in Europa und Asien weniger gefragt ist als in den USA.

Im Vergleich zu Chemisch Gold ist Chemisch Silber nur eingeschränkt bondbar und hat eine geringere Lagerfähigkeit.

Vorteile:

Sehr plane Oberfläche

Relativ kostengünstig

Nachteile:

Empfindliche Oberfläche

Nur eingeschränkt bondbar

Schlechte Lagerfähigkeit

- CHEMISCH ZINN

- CLIPPING

- COURYARD

- CTE

- CTI-WERT

- CU

Chemisch Zinn ist eine Leiterplattenoberfläche, die aufgrund ihrer erheblichen Nachteile nur noch selten verwendet wird.

Wegen der schnellen Oxidation des Kupfers erfordert diese Oberfläche eine genaue Überwachung der Temperatur und der Verpackung, was zu einem erhöhten Aufwand führt. Aus diesem Grund hat Beta LAYOUT Chemisch Zinn im PCB-Pool® abgekündigt. Diese Oberfläche ist jedoch weiterhin über PCB-OVERSEAS erhältlich.

Clipping bezeichnet das Beschneiden des Bestückungsdrucks, meist verursacht durch Fehler im Layout.

Wenn eine Bauteilbezeichnung im Layout beispielsweise teilweise über ein Pad gelegt wird, entfernt der Leiterplattenhersteller den überstehenden Teil beim DRC (Design Rule Check). Dies kann zu unleserlichen Bauteilbezeichnungen und ähnlichen Problemen führen.

Ein Courtyard (Hofraum) definiert den kleinsten erforderlichen Abstand um den tatsächlichen Umriss eines elektronischen Bauteils auf der Leiterplatte, bekannt als „Hofraumüberschuss“. Dies wird in der Leiterplatten-Designsoftware genutzt, um sicherzustellen, dass die Platine den Anforderungen des Design for Manufacturing (DFM) entspricht.

Der Courtyard legt einen Sicherheitsabstand um ein Bauteil fest, ähnlich einem Zaun um ein Gebäude. Dies soll sicherstellen, dass die Bauteile bei der Leiterplattenbestückung nicht zu eng nebeneinander platziert werden.

Der Courtyard wird als Teil der Footprint-Definition im Layoutprogramm erstellt.

CTE ist die Abkürzung für „Coefficient of Thermal Expansion“, zu deutsch Wärmeausdehnungskoeffizient. Der CTE spielt insbesondere bei Multilayern eine wichtige Rolle, da er beschreibt, wie sich Material unter Einfluss von Wärme ausdehnt.

In Multilayern werden viele verschiedene Schichten und Materialien mit unterschiedlichen Ausdehnungskoeffizienten verwendet. Eine ungleiche Verteilung von Kupfer in den Innenlagen kann beispielsweise zu unterschiedlichen CTEs führen und somit zur Verbiegung von Leiterplatten beitragen.

CTI steht für „Comparative Tracking Index“. Dieser Wert zeigt die Kriechstromfestigkeit des Leiterplattenmaterials an und wird in Volt (V) gemessen.

Je höher die Spannung, desto höher muss der CTI-Wert sein.

Die Details zum Messverfahren des CTI-Werts sind in der IEC 60112 festgelegt. Diese Norm beschreibt das Verfahren zur Bestimmung der Prüf- und Vergleichszahl der Kriechwegbildung von festen, isolierenden Werkstoffen.

Cu steht für →Kupfer

- ABFASEN

- ABSCHIRMUNG

- ABZIEHLACK

- ADAPTERTEST

- ÄTZEN

Abfasen, auch bekannt als „Anfasen“, beschreibt das Abschrägen oder Anfasen von Kanten an Leiterplattenkonturen.

Diese Technik wird beispielsweise bei Steckverbindern angewendet, um ein leichteres Verbinden mit der Leiterplatte zu ermöglichen.

Ein weiterer Grund für das Abflachen der Kanten kann der Schutz umliegender Komponenten vor scharfen Kanten während des Einbaus sein.

Abschirmungen sind Gehäuse, die eine Leiterplatte und/oder spezifische Bereiche in den Layouts der Leiterplatte umgeben, welche ein Masse- bzw. GND-Potenzial aufweisen. Ihr Zweck besteht darin, die Übertragung von Funkstörungen (RF) und elektromagnetischer Interferenzen (EMI) von einer Leiterbahn auf eine oder mehrere andere Leiterbahnen zu verhindern.

Bei Abschirmungen für Leiterplatten kann die Schirmung beispielsweise aus einer Leiterplatte mit einer integrierten Massefläche bestehen, sowie aus Metallgehäusen (sogenannten „Board Level Shieldings“ oder BLS), die über die empfindlichen oder sendenden Elemente gelegt werden. Diese Komponenten sind dann durch einen Faradayschen Käfig isoliert und bieten somit Abschirmungseffekte.

Abziehlacke, auch bekannt als Peelable Coating, finden vor allem Anwendung beim Wellenlöten oder Schwalllöten. Sie dienen dazu, ausgewählte Bereiche auf den Leiterplatten zu schützen, die mit einer Lötwelle in Kontakt kommen.

Der Abziehlack wird auf diese Bereiche aufgetragen, um den Kontakt mit Zinn zu verhindern. Falls anschließend ein weiteres Löten dieser Bereiche erforderlich ist, kann der Abziehlack später einfach entfernt werden.

Beim Adaptertest erfolgt die elektrische Prüfung von Leiterplatten mithilfe eines speziellen Adapters. Für diesen Test muss ein Nadeladapter eingerichtet werden, der auf die spezifische Leiterplatte abgestimmt ist.

Eine Alternative zum Adaptertest ist der Fingertest, auch als Flying Probe bekannt, der jedoch deutlich langsamer ist. Im Gegensatz dazu kann der Adaptertest auch bei bereits bestückten Leiterplatten durchgeführt werden. Allerdings rentiert sich der Bau eines Adapters für den Adaptertest aufgrund des höheren Aufwands und der Kosten erst bei größeren Serien.

Ätzen ist ein Verfahren, das dazu dient, den Teil der Platine, der nicht von einer Resist-Schicht bedeckt ist, vom leitfähigen Material, meist Kupfer, zu entfernen. Dies geschieht entweder durch alkalisches Ätzen mittels Ammoniak oder saures Ätzen mit Eisen-III-Chlorid.

Vorbereitung der Platine: Zuerst wird die Platine vorbereitet, indem sie mit einer Resist-Schicht bedeckt wird. Diese Resist-Schicht schützt die Bereiche der Platine, die nicht geätzt werden sollen, vor dem Ätzmittel.

Ätzmittel anwenden: Das Ätzmittel, entweder Ammoniak für alkalisches Ätzen oder Eisen-III-Chlorid für saures Ätzen, wird auf die Platine aufgetragen. Das Ätzmittel greift das ungeschützte Kupfer an und entfernt es von der Oberfläche der Platine.

Entfernen der Resist-Schicht: Nach dem Ätzen wird die Resist-Schicht von der Platine entfernt, um die Leiterbahnen und Verbindungen freizulegen.

Reinigung: Abschließend wird die Platine gründlich gereinigt, um jegliche Rückstände des Ätzmittels zu entfernen und eine saubere Oberfläche zu gewährleisten.

- ATZRESIST

- ALUKERN PLATINEN

- ALUMINIUM KERN

- ANNULAR RING

- ANTI-PAD

Ätzresist ist das Material, das die Leiterbahnen, in der Regel aus Kupfer, vor dem Einwirken der Ätzflüssigkeit wie Ammoniak oder Eisen-III-Chlorid schützt.

Vgl. auch Resist

Alukern-Platinen, auch bekannt als IMS-Leiterplatten, sind ein- oder mehrschichtige Leiterplatten, die Aluminiumschichten im Inneren enthalten. Die Verwendung von Aluminiumkernleiterplatten ermöglicht die Integration von Kühlkörpern direkt in die Platine. Dadurch wird die erzeugte Wärme besser verteilt und abgeleitet als beispielsweise bei einer FR4-Leiterplatte.

Das Durchkontaktieren wird durch Vorbohren und Isolieren des Aluminiumträgers realisiert.

Alukern-Platinen finden hauptsächlich Anwendung in der LED-Technik und bei Hochleistungskomponenten, die eine starke Wärmeentwicklung aufweisen.

Ein Aluminiumkern ist eine in mehrschichtigen Aluminiumkern-Leiterplatten integrierte Aluminiumschicht, die dazu dient, die Wärme abzuleiten, die während des Betriebs der Bauteile entsteht.

Ein Annular Ring ist der ringförmige Bereich um eine Durchkontaktierung (auch als Via bezeichnet) auf einer Leiterplatte. Es ist der Abstand zwischen dem Rand der Durchkontaktierung und dem Rand des umgebenden Pads oder Lötaugens. Der Annular Ring spielt eine wichtige Rolle für die Zuverlässigkeit und Qualität der Durchkontaktierung, da er die elektrische Verbindung zwischen den Leiterbahnen auf verschiedenen Ebenen der Leiterplatte gewährleistet und die mechanische Stabilität der Durchkontaktierung beeinflusst. Ein ausreichend großer Annular Ring ist wichtig, um eine sichere Lötverbindung herzustellen und gleichzeitig genügend Platz für das Bohren und Herstellen der Durchkontaktierung zu bieten.

Vgl. auch Restring

Ein Anti-Pad bezeichnet eine unbestückte, freie Fläche auf einer Leiterplatte um eine Durchkontaktierung herum. Diese Fläche ist normalerweise mit Isolationsmaterial bedeckt und dient dazu, einen Abstand zwischen einer Durchkontaktierung und anderen leitenden Elementen auf der Leiterplatte zu gewährleisten, um Kurzschlüsse zu vermeiden. Das Anti-Pad sorgt dafür, dass keine elektrische Verbindung zwischen der Durchkontaktierung und den benachbarten Leiterbahnen oder Pads hergestellt wird. Es wird auch als Isolationsbereich oder Schutzbereich um eine Durchkontaktierung herum bezeichnet. Die Größe und Form des Anti-Pads können je nach den Anforderungen des Designs und den Spezifikationen der Leiterplatte variieren.

Vgl. auch Pad-Freistellung

- AOI

- ARC RESISTANCE

- ASPECT-RATIO

- AU

- AUFBAU

Au (Aurum) ist das chemische Symbol für Gold. In der Herstellung von Leiterplatten spielt Gold eine wichtige Rolle bei der Oberflächenveredelung der Platte.

Vgl. auch Gold

Arc Resistance bezieht sich auf die Fähigkeit des Isolationsmaterials auf der Leiterplatte, einen Lichtbogen zu widerstehen. Lichtbögen können auftreten, wenn es zu einem Kurzschluss oder einer Überlastung kommt, was zu einer elektrischen Entladung führt. Dieser Lichtbogen kann das Isolationsmaterial beschädigen oder zerstören, was zu einem Ausfall der Leiterplatte oder sogar zu einem Brand führen kann.

Daher ist die Arc Resistance ein wichtiger Parameter bei der Auswahl des Isolationsmaterials für Leiterplatten. Materialien mit hoher Arc Resistance bieten eine bessere Sicherheit und Zuverlässigkeit, da sie einem Lichtbogen widerstehen können, ohne beschädigt zu werden. Dies ist besonders wichtig in Anwendungen, in denen hohe Spannungen oder Ströme vorhanden sind, wie beispielsweise in der Leistungselektronik oder in Hochspannungsanwendunge.

Vgl. auch Lichtbogenfestigkeit

Aspect-Ratio (AR, englisch für „Seitenverhältnis“) bezieht sich bei Leiterplatten auf das Verhältnis zwischen der Tiefe eines gebohrten Lochs und dem Durchmesser des Bohrwerkzeugs, das für dieses Loch verwendet wird.

Die Formel lautet: Aspect-Ratio = Durchmesser des Bohrwerkzeugs (in Mikrometer) : Tiefe des Lochs, die kontaktiert werden kann (in Mikrometer)

Die Tiefe des Lochs wird ohne Berücksichtigung von Kupferbeschichtung, Lötmaske, Oberflächenbehandlung oder Positionierungsmarkierungen angegeben. Ein höheres Verhältnis macht es schwieriger, eine zuverlässige Beschichtung zu erreichen, und erhöht das Risiko von Rissen während der Bestückung der Leiterplatte aufgrund der Materialausdehnung.

Bei einem niedrigeren Verhältnis sind die Durchkontaktierungen robuster und bieten eine bessere elektrische Verbindung.

Mit Hilfe des Aspect-Ratio kann bei einem festgelegten Bohrungsdurchmesser auch die passende Leiterplattendicke berechnet werden.

Aspect-Ratio (AR, englisch für „Seitenverhältnis“) bezieht sich bei Leiterplatten auf das Verhältnis zwischen der Tiefe eines gebohrten Lochs und dem Durchmesser des Bohrwerkzeugs, das für dieses Loch verwendet wird.

Die Formel lautet: Aspect-Ratio = Durchmesser des Bohrwerkzeugs (in Mikrometer) : Tiefe des Lochs, die kontaktiert werden kann (in Mikrometer)

Die Tiefe des Lochs wird ohne Berücksichtigung von Kupferbeschichtung, Lötmaske, Oberflächenbehandlung oder Positionierungsmarkierungen angegeben. Ein höheres Verhältnis macht es schwieriger, eine zuverlässige Beschichtung zu erreichen, und erhöht das Risiko von Rissen während der Bestückung der Leiterplatte aufgrund der Materialausdehnung.

Bei einem niedrigeren Verhältnis sind die Durchkontaktierungen robuster und bieten eine bessere elektrische Verbindung.

Mit Hilfe des Aspect-Ratio kann bei einem festgelegten Bohrungsdurchmesser auch die passende Leiterplattendicke berechnet werden.

Der Aufbau von Leiterplatten kann je nach den Anforderungen des Designs variieren, aber im Allgemeinen bestehen Leiterplatten aus mehreren Lagen von Substratmaterial, die mit leitfähigen Kupferbahnen bedruckt sind. Hier ist ein typischer Aufbau für eine mehrschichtige Leiterplatte:

Innere Lagen: Diese Lagen bestehen aus einem isolierenden Substratmaterial, das oft aus Glasfaserverbundwerkstoff (FR-4) besteht. Auf beiden Seiten des Substrats sind Kupferbahnen aufgedruckt, die durch einen Prozess der Fotolithographie und Ätzung hergestellt werden. Diese inneren Lagen enthalten oft die Hauptverbindungen und Schaltungen des Designs.

Dielektrisches Material: Zwischen den inneren Lagen befindet sich dielektrisches Material, das isolierend ist und die elektrischen Verbindungen zwischen den einzelnen Lagen trennt. Dieses Material kann auch als Prepreg bezeichnet werden und ist in der Regel ein Epoxidharz.

Äußere Lagen: Auf beiden Seiten der inneren Lagen befinden sich die äußeren Lagen. Diese bestehen aus dem gleichen isolierenden Substratmaterial wie die inneren Lagen und sind ebenfalls mit Kupferbahnen bedruckt. Die äußeren Lagen enthalten oft die Anschlüsse und Schnittstellen, die mit externen Komponenten verbunden sind.

Kupferbeschichtung: Nachdem die Leiterplatte geätzt wurde, um die gewünschten Leiterbahnen zu formen, wird die gesamte Oberfläche der Leiterplatte normalerweise mit einer dünnen Schicht Kupfer beschichtet, um die Lötbarkeit zu verbessern und die Leiterbahnen zu schützen.

Lötmaske und Beschriftung: Eine Lötmaske wird über die Leiterplatte aufgebracht, um die Leiterbahnen abzudecken und sie während des Lötprozesses zu schützen. Darüber hinaus kann eine Beschriftung aufgedruckt werden, um die Komponenten zu identifizieren und das Layout zu erleichtern.

Vgl. auch Lagenaufbau

- AUSFRÄSEN

- AUSSENLAGE

- AUTOROUTER

Das Ausfräsen von Leiterplatten ist ein Verfahren, bei dem überschüssiges Material um den Umfang der Leiterplatte entfernt wird, um die Leiterplatte in die gewünschte Form zu bringen. Hier sind die Schritte für das Ausfräsen von Leiterplatten:

Vorbereitung der Leiterplatte: Zunächst wird die Leiterplatte vorbereitet, indem sie in einem größeren Panel hergestellt wird. Dieses Panel kann mehrere Leiterplatten enthalten, die später einzeln ausgeschnitten werden.

Programmierung: Ein CAD-Programm wird verwendet, um die Konturen der Leiterplatten festzulegen, die aus dem Panel ausgeschnitten werden sollen. Dieses Programm erstellt eine digitale Vorlage, die den Fräsern sagt, wo sie schneiden sollen.

Fräsen: Die Leiterplatten werden in eine Fräsmaschine geladen, die mit speziellen Fräswerkzeugen ausgestattet ist. Die Maschine liest die digitale Vorlage und führt dann präzise Schnitte entlang der vorgegebenen Konturen durch, um die Leiterplatten aus dem Panel herauszutrennen.

Entgraten und Reinigen: Nach dem Fräsen werden die Kanten der Leiterplatten oft entgratet, um scharfe Kanten zu entfernen. Anschließend werden die Leiterplatten gründlich gereinigt, um überschüssigen Staub und Rückstände zu entfernen.

Inspektion: Abschließend werden die ausgeschnittenen Leiterplatten inspiziert, um sicherzustellen, dass sie den Spezifikationen entsprechen und frei von Fehlern sind.

Das Ausfräsen von Leiterplatten ist ein wichtiger Schritt im Herstellungsprozess, der dazu beiträgt, dass die Leiterplatten die gewünschte Form und Größe haben, um in elektronischen Geräten verwendet zu werden.

Vgl. auch Fräsen

Die Außenlage bezeichnet die obere (Top) oder untere (Bottom) Schicht einer mehrschichtigen Leiterplatte.

Eine Leiterplatte kann entweder eine oder zwei Außenlagen haben, auf denen später Komponenten montiert werden können.

In jeder modernen Leiterplatten-Layoutsoftware ist ein Autorouter enthalten, der automatisch die tatsächliche Strukturierung der Leiterplatte aus einem Schaltplan generiert. Die Verbindungen zwischen den Komponenten werden in der Regel als Ratsnest dargestellt und müssen entwirrt werden.

Das Routing, also das Verlegen der Leiterbahnen zur Verbindung der Komponenten, wird automatisch durchgeführt, wobei die Designregeln (Design Roules) beachtet werden. Oft erfolgt dieser Vorgang auch interaktiv, was bedeutet, dass der Leiterplattendesigner regelmäßig in den Autorouter eingreift.

- BELICHTEN

- BESTÜCKUNG

- BESTÜCKUNGSDRUCK

- BESTÜCKUNGSPLAN

- BESTÜCKUNGSSEITE

Das Belichten ist vor allem in der traditionellen Leiterplattenherstellung erforderlich. Es wird sowohl beim Belichten des →Resists vor dem Ätzen als auch beim Belichten des Lötstopplacks nach dessen Aufbringen auf die Platine angewendet.

Heutzutage werden meist →Direktbelichter verwendet, die das Leiterplattenbild direkt auf die zu belichtende Platte projizieren, wodurch der Einsatz eines Films zur Belichtung überflüssig wird

Bestückung bezeichnet das Anbringen von Komponenten auf der Leiterplatte. Die Leiterplatte dient dabei als Basis und fungiert als Träger der Bauteile und Verbindungselemente.

Der Bestückungsdruck bezieht sich auf eine Farbe (Lack), die verwendet wird, um Positionen, Beschriftungen und Abbildungen auf der Leiterplatte anzubringen. Er wird auch häufig als Positionsdruck (Posi) oder Kennzeichnungsdruck bezeichnet. In den meisten Fällen wird Weiß für den Bestückungsdruck verwendet, obwohl auch andere Farben wie Schwarz, Rot, Gelb, Grün usw. verfügbar sind.

Der Bestückungsdruck auf einer Leiterplatte von PCB Beta LAYOUT kennzeichnet die Umrisse der Bauteile und ihre Bezeichnung. Er wird in der Regel entweder durch Siebdruckverfahren oder mit einem speziellen Tintenstrahldrucker aufgetragen. Diese Methoden ermöglichen auch kostengünstige Einzelstückbedruckungen, da kein Film benötigt wird.

Normalerweise werden nur die Umrisse der Bauelemente gedruckt, um das manuelle Bestücken zu erleichtern, sowie die Bezeichnung der einzelnen Bauteile (z. B. Durchnummerierung), um sie bei Reparaturen mithilfe des Schaltplans zu identifizieren. Auch Logos oder CE-Zeichen sind beliebt.

Siehe Bauteilseite

Siehe auch Bauteilseite

- BEVELING

- BGA

- BIEGEFESTIGKEIT

- BILL OF MATERIALS

- BLACK PAD

Beveling ist die englische Bezeichnung für das Abfasen oder Anfasen.

BGA (Ball Grid Array) sind eine modernere Variante von SMD-Bauteilen, bei der die Anschlüsse für die SMD-Bestückung kompakt auf der Unterseite des Bauteils angeordnet sind.

Diese Anschlüsse bestehen aus kleinen Lotperlen (englisch „balls“), die in einem regelmäßigen Raster (englisch „grid“) angeordnet sind, ähnlich einer Matrix mit Spalten und Zeilen (englisch „array“).

Beim Reflow-Löten werden diese Lotperlen geschmolzen und verbinden sich mit den Kontaktpads auf der Leiterplatte. Der Hauptvorteil liegt in der Platzersparnis, da eine größere Anzahl von Anschlüssen platziert werden kann, da sie unterhalb des Bauteils anstatt an den Seiten angeordnet sind.

Dies erschwert jedoch die spätere Überprüfung der Lötstellen, da diese nur noch durch Röntgenkontrolle überprüft werden können.

Die Biegefestigkeit, auch bekannt als Querbruchfestigkeit, bezeichnet die Spannung, die das PCB-Material aushalten kann, ohne zu brechen, wenn es in der Mitte belastet wird und auf beiden Seiten aufliegt.

Besonders bei flexiblen Leiterplatten ist die Biegefestigkeit von Bedeutung, da dort Biegeradien und die generelle Flexibilität entscheidend sind.

Die Biegefestigkeit wird in Einheiten wie kg/m2 oder psi gemessen.

Die Bauteilliste für die Bestückung von Leiterplatten, auch bekannt als BOM (Bill of Materials), ist eine Aufstellung aller benötigten Komponenten.

Black Pad, auch als „schwarzes Pad“ bezeichnet, tritt auf, wenn Chemisch Gold als Oberflächenbeschichtung auf Leiterplatten aufgebracht wird.

In solchen Fällen kann es vorkommen, dass einige Pads sich schwarz verfärben und sich nur schwer oder gar nicht löten lassen.

Ursache dafür ist eine Korrosion der Nickelschicht, die sich unter dem Gold befindet. Diese Korrosion ist vor der Bestückung mit bloßem Auge oft nicht erkennbar.

- BLASENBILDUNG

- BLEI

- BLEIFREI

- BLIND VIA

- BOHRABSTAND

Blasenbildung:

siehe auch → Delamination

Blei (chemisch „Pb“, Plumbum) oder „lead“ (Englisch) ist ein Metall, das häufig als Bestandteil von Lotlegierungen verwendet wird. Aufgrund der Einführung der →RoHS/WEEE-Norm wurde Blei größtenteils als Legierungsbestandteil verboten, da es giftig ist. Insbesondere die Dämpfe beim Löten stellen eine erhebliche Gesundheitsgefahr dar.

Heutzutage wird verbleites Lot für Leiterplatten in der Regel nur noch auf ausdrücklichen Kundenwunsch geliefert. Seit 2015 ist der Einsatz von bleihaltigem Lot in den meisten Produkten verboten und nur noch in spezifischen Anwendungsfällen gesetzlich erlaubt. Dazu gehören bestimmte Komponenten in der Automobiltechnik, Medizintechnik und Photovoltaikanlagen sowie in der Luft- und Raumfahrt, dem militärischen Bereich sowie in Forschung und Entwicklung.

Auch Hobbyanwender dürfen bleihaltiges Lot verwenden, solange sie ihre Geräte nicht in den Handel bringen.

Die Einführung von bleifreiem Lot erfolgte im Jahr 2006 und ist heute für die meisten elektronischen Anwendungen obligatorisch. Es gibt jedoch Ausnahmen für bestimmte Branchen, in denen weiterhin bleihaltiges Lot verwendet werden darf.

Die Herstellung von bleifreien Leiterplatten ist mittlerweile Standard in der Leiterplattenproduktion. Die Prozesse und verwendeten Materialien wurden erfolgreich an die vor allem höheren Löttemperaturen angepasst.

Blind Vias sind Bohrungen in der Leiterplatte, die eine Außenlage mit Innenlagen verbinden. Da sie nicht die gesamte Materialdicke durchdringen, werden sie auch als „Sacklöcher“ bezeichnet.

Diese Vias sind daher von einer Seite aus nicht sichtbar. Je nach Bohrdurchmesser und Tiefe (siehe →Aspekt-Ratio) bringen Blind Vias unterschiedliche Herausforderungen mit sich.

Wenn Innenlagen miteinander verbunden sind, ohne Kontakt nach außen zu haben, spricht man von „Buried Vias“.

Der Begriff Bohrabstand bezieht sich auf den Abstand zwischen zwei Bohrungen auf einer Leiterplatte.

Der Bohrabstand ist ein entscheidendes Merkmal, da bei Unterschreitung der Mindestabstände der Steg zwischen den Bohrungen brechen kann.

Beim Bohren besteht immer eine gewisse Toleranz. Der Bohrer kann durch Bestandteile des Laminats (wie Glasgewebe, Gewebe oder Keramik) abgelenkt werden, was zu einer Verschiebung der Bohrposition führt und den Bohrer möglicherweise zu nah an eine benachbarte Bohrung bringen kann.

Diese Möglichkeit sollte bereits während des Designs berücksichtigt werden, indem man sich an die in den Designregeln festgelegten Abstände hält und ausreichend große Abstände wählt.

Die minimale Distanz beträgt bei den meisten Leiterplattenherstellern etwa 0,2 mm, obwohl dies von Hersteller zu Hersteller variieren kann. Auch die Bohrtechnik spielt eine Rolle, da bei NDK-Bohrungen der Bohrabstand kleiner sein kann.

- BOHREN

- BOHRPROGRAMM

- BOHRUNG

- BOM

- BOTTOM

Das Bohren ist erforderlich für die Herstellung von Fanglöchern, Durchkontaktierungen und Bauteilbohrungen auf Leiterplatten. Es ermöglicht die Verbindung der Schichten (Lagen) und das Einsetzen von Bauteilen zu einem späteren Zeitpunkt.

Bei ein- und doppelseitigen Leiterplatten erfolgt dieser Prozess unmittelbar nach dem Zuschnitt. Bei mehrschichtigen Leiterplatten hingegen erfolgt das Bohren erst nach der Laminierung. Zunächst müssen die Innenlagen strukturiert und verpresst werden, bevor sie gebohrt werden können.

Das Bohrprogramm ist eine ASCII-Textdatei, die durch die IPC-Norm NC-349 (Computer Numerical Control Formatting for Drillers and Routers) definiert wird. Es übermittelt dem Bohrer die Koordinaten und Durchmesser der zu bohrenden Löcher auf der Leiterplatte. Zusätzlich enthält es Informationen über die Werkzeuge, die für die verschiedenen Bohrungen verwendet werden sollen. Das Bohrprogramm wird aus dem Layout der Leiterplatte abgeleitet, das die Position und Form der Bauteile und Leiterbahnen zeigt. Typischerweise wird das Bohrprogramm im Format Excellon oder Sieb & Meyer exportiert, das von den meisten Bohrmaschinen erkannt wird.

Bei der Bereitstellung von Gerber-Daten müssen diese Dateien zusammen mit den Gerberdaten an den Leiterplattenhersteller übermittelt werden.

BOM steht für „Bill Of Materials“ und bezieht sich auf die Bauteilliste für die Bestückung von Leiterplatten.

Die Erstellung der BOM kann oft zeitaufwändig sein, da die Bauteile gesucht und bestellt werden müssen.

BOM steht für „Bill Of Materials“ und bezieht sich auf die Bauteilliste für die Bestückung von Leiterplatten.

Die Erstellung der BOM kann oft zeitaufwändig sein, da die Bauteile gesucht und bestellt werden müssen.

Bottom bezeichnet die „Unterseite“ von Leiterplatten, die früher oft als Lötseite bezeichnet wurde. Damals wurden jedoch ausschließlich THT-Bauteile auf dieser Seite der Leiterplatte gelötet.

Mit der Einführung von SMD-Bauteilen ist der Begriff „Lötseite“ nicht mehr eindeutig, und „Bottom“ ist daher eine klarere Bezeichnung.

- BREAKOUT

- BURIED VIA

Breakout ist der englische Begriff für „Ausbruch“ und bezieht sich auf Bohrungen auf einer Leiterplatte, die nicht zentriert auf dem vorgesehenen Pad liegen und daraus resultieren. Für durchkontaktierte Pads (DK) ist ein ausreichender Restring erforderlich, um eine ordnungsgemäße Lötbarkeit sicherzustellen. Die Größe des Rings im Design sollte groß genug sein, um Abweichungen des Bohrers von der Mitte des Lochs auszugleichen. Wenn das Pad zu klein ist, kann es zu einem Ausbruch kommen, was zu unterbrochenen, unvollständigen Schaltungen oder unsachgemäßem Löten führen kann. Daher sehen Leiterplattenhersteller vor, dass der Restring um eine Durchkontaktierung einen größeren Durchmesser als der Bohrer haben muss, um mögliche Breakouts abzufangen.

In einigen Fällen kann ein Teardrop die Toleranz des Bohrers im Pad erhöhen, was dazu beitragen kann, den Ausschuss bei der Leiterplattenproduktion zu verringern.

Ein Buried Via (auch bekannt als vergrabene Durchkontaktierung oder vergrabene Bohrung) ist eine Durchkontaktierung innerhalb einer Leiterplatte, die mindestens zwei Innenlagen eines Multilayers miteinander verbindet, ohne die Außenlagen zu durchdringen.

Wie der Name schon sagt, ist eine vergrabene Durchkontaktierung von außen nicht erkennbar. Diese Vias können vor dem Verpressen des Multilayers gebohrt, durchkontaktiert und anschließend verschlossen werden.

Buried Vias ermöglichen eine höhere Packungsdichte, was bedeutet, dass auf einer gleichbleibenden Fläche mehr Funktionen integriert werden können. In einer Zeit, in der die Miniaturisierung immer weiter voranschreitet, kann dies ein wesentlicher Vorteil sein.

Allerdings können erhöhte Kosten entstehen, da die Produktion einen erhöhten Aufwand erfordert und zusätzliche Tests notwendig sind.

- CAD

- CAF-RESISTENZ

- CAM

- CARBON

- CASTELLATED-HOLS

CAD steht für „Computer Aided Design“. Früher wurden Leiterplatten manuell entworfen, aber heutzutage werden dafür Computer und spezielle CAD-Software verwendet. Nach dem Entwurf werden die produktionsfertigen Daten mithilfe von CAM erstellt. Anschließend erfolgt die Fertigung der Leiterplatte.

Beliebte CAD-Programme sind unter anderem EAGLE, Altium, TARGET 3001!, Autodesk Fusion 360, KiCad und viele andere.

Die Resistenz gegenüber CAF (Conductive Anodic Filament) oder CAF-Beständigkeit beschreibt die Fähigkeit eines Materials, das isoliert ist (zum Beispiel FR4), die elektromechanische Migration von metallisierten Salzen zu verhindern.

CAF bezieht sich auf die Bildung leitfähiger Verbindungen zwischen zwei Potenzialen von der Anode zur Kathode, die durch die Migration von Kupferionen entlang von Glasfasern innerhalb von Leiterplatten entsteht.

Dies kann zur Bildung von leitfähigen Pfaden und in extremen Fällen zu Kurzschlüssen führen.

Dieser Effekt tritt insbesondere bei fortschreitender Miniaturisierung und Komplexität der Leiterplatten auf und seine Erkennung und Beseitigung ist schwierig.

CAM (Computer Aided Manufacturing) bildet den Zwischenschritt zwischen der elektronischen Entwurfsphase (CAD) und dem tatsächlich hergestellten Objekt.

Die gelieferten Daten müssen in ein für die Produktion geeignetes Format umgewandelt und auf mögliche Fehler überprüft werden. Hierfür steht spezielle Software zur Verfügung.

In der Regel wird „Carbon“ als Abkürzung für „Carbon Print“ oder „Karbondruck“ verwendet. Dabei handelt es sich um ein Verfahren, bei dem Carbonlack mithilfe von Siebdruck auf die Leiterplatte aufgetragen wird.

Aufgrund seiner leitenden Eigenschaften und der hohen Härte des Materials wird Carbonlack beispielsweise als Beschichtung für Drucktaster auf der Leiterplatte eingesetzt.

engl. Bezeichnung für →Halboffene Durchkontaktierung

- CE-KENNZEICHNUNG

- CE-KONFORMITÄTSERKLÄRUNG

- CHEMISCH GOLD

- CHEMISCH NICKEL/GOLD

- CHEMISCH SILBER

Durch die CE-Kennzeichnung erklärt der Hersteller, Inverkehrbringer oder EU-Bevollmächtigte gemäß Verordnung (EG) Nr. 765/2008, dass das Produkt den geltenden Anforderungen entspricht, die in den Harmonisierungsrechtsvorschriften der Gemeinschaft über die Anbringung festgelegt sind (Artikel 2 Nummer 20). Außerdem übernimmt er die Verantwortung dafür, dass das Produkt gemäß den einschlägigen Harmonisierungsrechtsvorschriften der Gemeinschaft konform ist (Artikel 30 Absatz 3).

Die mit CE gekennzeichneten Produkte wurden jedoch nicht von einer unabhängigen Stelle überprüft. Derjenige, der das CE-Zeichen verwendet, bestätigt lediglich selbst die Konformität seines Produkts mit den einschlägigen Vorschriften.

Für die Inverkehrbringung eines Produktes in Deutschland ist eine CE-Konformitätserklärung erforderlich

Die CE-Konformitätserklärung ist eine schriftliche Bestätigung des Herstellers, dass ein Produkt die Anforderungen aller relevanten CE-Richtlinien erfüllt.

Für jedes Produkt, das unter eine EU-Richtlinie fällt, ist eine solche Erklärung notwendig. Der Hersteller muss die CE-Konformitätserklärung als Teil der technischen Dokumentation aufbewahren und auf Anfrage einer Aufsichtsbehörde vorlegen können.

Chemisch Gold, auch als Chemisch Nickel/Gold (ENIG) bekannt, ist eine Leiterplattenoberfläche. Mit der steigenden Nachfrage nach feineren Leiterbahnen und der zunehmenden Packungsdichte auf Leiterplatten wird HAL (Hot Air Leveling) immer ungeeigneter.

Chemisch Gold bietet eine hervorragende Alternative. Diese Oberfläche ist sehr plan und hat ausgezeichnete Oxidationseigenschaften. Die Zusammensetzung von Chemisch Gold beträgt 3-5 μm Nickel und 0,05-0,1 μm Gold.

Vorteile:

Sehr gut für Finepitch geeignet

Hervorragend für SMD geeignet

Sehr plane Pads, die mit HAL nicht erreicht werden können

Sehr gute Benetzbarkeit

Die Nickelschicht verstärkt mechanisch die Durchkontaktierungen und Vias und erhöht die Abriebfestigkeit

Gute Lagerfähigkeit (ca. 1 Jahr)

Nachteile:

- Höhere Kosten im Vergleich zu HAL

→Chemisch Gold

Chemisch Silber

Chemisch Silber ist eine Leiterplattenoberfläche, die Chemisch Zinn ähnelt, jedoch eine geringere Oxidation aufweist. Trotz dieser Eigenschaft ist Chemisch Silber ähnlich empfindlich, weshalb es in Europa und Asien weniger gefragt ist als in den USA.

Im Vergleich zu Chemisch Gold ist Chemisch Silber nur eingeschränkt bondbar und hat eine geringere Lagerfähigkeit.

Vorteile:

Sehr plane Oberfläche

Relativ kostengünstig

Nachteile:

Empfindliche Oberfläche

Nur eingeschränkt bondbar

Schlechte Lagerfähigkeit

- CHEMISCH ZINN

- CLIPPING

- COURYARD

- CTE

- CTI-WERT

- CU

Chemisch Zinn ist eine Leiterplattenoberfläche, die aufgrund ihrer erheblichen Nachteile nur noch selten verwendet wird.

Wegen der schnellen Oxidation des Kupfers erfordert diese Oberfläche eine genaue Überwachung der Temperatur und der Verpackung, was zu einem erhöhten Aufwand führt. Aus diesem Grund hat Beta LAYOUT Chemisch Zinn im PCB-Pool® abgekündigt. Diese Oberfläche ist jedoch weiterhin über PCB-OVERSEAS erhältlich.

Clipping bezeichnet das Beschneiden des Bestückungsdrucks, meist verursacht durch Fehler im Layout.

Wenn eine Bauteilbezeichnung im Layout beispielsweise teilweise über ein Pad gelegt wird, entfernt der Leiterplattenhersteller den überstehenden Teil beim DRC (Design Rule Check). Dies kann zu unleserlichen Bauteilbezeichnungen und ähnlichen Problemen führen.

Ein Courtyard (Hofraum) definiert den kleinsten erforderlichen Abstand um den tatsächlichen Umriss eines elektronischen Bauteils auf der Leiterplatte, bekannt als „Hofraumüberschuss“. Dies wird in der Leiterplatten-Designsoftware genutzt, um sicherzustellen, dass die Platine den Anforderungen des Design for Manufacturing (DFM) entspricht.

Der Courtyard legt einen Sicherheitsabstand um ein Bauteil fest, ähnlich einem Zaun um ein Gebäude. Dies soll sicherstellen, dass die Bauteile bei der Leiterplattenbestückung nicht zu eng nebeneinander platziert werden.

Der Courtyard wird als Teil der Footprint-Definition im Layoutprogramm erstellt.

CTE ist die Abkürzung für „Coefficient of Thermal Expansion“, zu deutsch Wärmeausdehnungskoeffizient. Der CTE spielt insbesondere bei Multilayern eine wichtige Rolle, da er beschreibt, wie sich Material unter Einfluss von Wärme ausdehnt.

In Multilayern werden viele verschiedene Schichten und Materialien mit unterschiedlichen Ausdehnungskoeffizienten verwendet. Eine ungleiche Verteilung von Kupfer in den Innenlagen kann beispielsweise zu unterschiedlichen CTEs führen und somit zur Verbiegung von Leiterplatten beitragen.

CTI steht für „Comparative Tracking Index“. Dieser Wert zeigt die Kriechstromfestigkeit des Leiterplattenmaterials an und wird in Volt (V) gemessen.

Je höher die Spannung, desto höher muss der CTI-Wert sein.

Die Details zum Messverfahren des CTI-Werts sind in der IEC 60112 festgelegt. Diese Norm beschreibt das Verfahren zur Bestimmung der Prüf- und Vergleichszahl der Kriechwegbildung von festen, isolierenden Werkstoffen.

Cu steht für →Kupfer

Thermische Probleme, Leckströme und die stetige Suche nach neuen Materialien und Technologien bilden die Herausforderungen der Elektronikfertigung.

Trends in der Branche beinhalten die Erforschung von Quantenpunkten, 3D-Integration und neuartigen Materialien.

Dementsprechend arbeitet die Elektronikfertigung an Technologien wie der Quantencomputerentwicklung, die die herkömmliche Transistorarchitektur möglicherweise in Zukunft revolutionieren könnten.

Haben wir Ihr Interesse geweckt? Wir begleiten Sie gerne, geht es darum, die Integration von innovativer Elektronik in den Alltag zu ermöglichen.

Die Erfindung des Transistors hat die Elektronik revolutioniert

In der Elektronikfertigung spielen Transistoren eine entscheidende Rolle, da sie als grundlegende Bauelemente in nahezu allen elektronischen Geräten verwendet werden. Hier sind einige wissenswerte Informationen über Transistoren in der Elektronikfertigung

Meilensteine in der Entwicklung der Elektronik

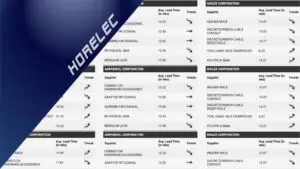

Innovative Ansätze in der Leistungselektronik und ein klarer Fokus auf die Bedürfnisse unserer Kunden, ihre Leistung in diesen Schlüsselbereichen zu verbessern, sind Hauptanliegen von HORELEC. Trends der Zukunft als …

Engpässe auf dem Halbleitermarkt? Ein Update.

Grundsätzlich geben wir als Bestücker die Gerberdaten vom Kunden an den Leiterplattenhersteller weiter. Wir als Bestücker sehen diese Daten nicht ein und ändern auch nichts daran.

Es gibt viele Feinheiten bei der Herstellung einer Leiterplatte, welche wir nicht kennen können.

Vom Prototypen zur Serienproduktion

Grundsätzlich geben wir als Bestücker die Gerberdaten vom Kunden an den Leiterplattenhersteller weiter. Wir als Bestücker sehen diese Daten nicht ein und ändern auch nichts daran.

Es gibt viele Feinheiten bei der Herstellung einer Leiterplatte, welche wir nicht kennen können.

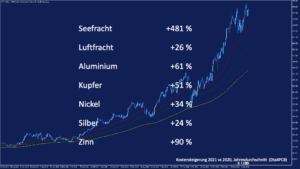

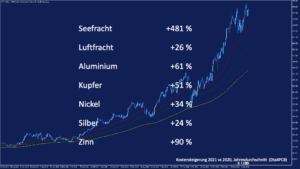

Ausblick Halbleitermarkt 2023

Ausblick bzgl. der aktuellen, weltweiten Situation im Halbleiter-Markt mit näheren Angaben zu Lieferzeiten und Preiserhöhungen marktrelevanter Hersteller.

Rohstoffe der EMS

Organische als auch anorganische Rohstoffe spielen in der EMS eine entscheidende Rolle. So gelten Eisenmetalle als auch Nicht-Eisenmetalle als die Grundmaterialen der EMS. Die Rede ist von Kupfer, Aluminium, …

EMS – Trends für die Zukunft

Innovative Ansätze in der Leistungselektronik und ein klarer Fokus auf die Bedürfnisse unserer Kunden, ihre Leistung in diesen Schlüsselbereichen zu verbessern, sind Hauptanliegen von HORELEC. Trends der Zukunft als …

Halbleitermarkt 2022

Ausblick bzgl. der aktuellen, weltweiten Situation im Halbleiter-Markt mit näheren Angaben zu Lieferzeiten und Preiserhöhungen marktrelevanter Hersteller.

Kritische Versorgungslage in der Elektronik

Nach der Pandemie steht die Wirtschaft auf Wachstum. Leider steht hier jedoch folgendes im Weg: Die Versorgung schafft die Kurve nicht. Wie begegnen wir dieser Situation? Es mangelt an der Lieferung von Rohstoffen und Komponenten für die Elektronikfertigung.

Rohstoffe der EMS

Organische als auch anorganische Rohstoffe spielen in der EMS eine entscheidende Rolle. So gelten Eisenmetalle als auch Nicht-Eisenmetalle als die Grundmaterialen der EMS. Die Rede ist von Kupfer, Aluminium, …